Shadow Transistors

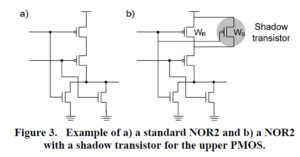

Device scaling has enabled continuous performance increase of integrated circuits. However, severe reliability and yield concerns are arising against the background of nanotechnology. Traditionally, most causes and countermeasures were solely considered manufacturing issues, but lately, we have seen a shift towards operational reliability issues. Though, besides intense research on soft-errors and system-level approaches very little effort is put into low-level design solutions in order to enhance lifetime reliability. Hence, we demonstrate that redundant transistor insertion does improve system reliability significantly as regards Time-Dependent Dielectric Breakdown (TDDB). Furthermore, we introduce an algorithm which identifies the transistors being most vulnerable to TDDB. Subsequently, redundant transistors – called Shadow Transistors – are inserted at the previously identified instances. Lastly, we argue for applying high threshold voltage devices for the redundant transistors. Finally, we present results for a set of benchmark circuits and prove the combined approach successful. The enhanced designs were on average 41.8 % more reliable compared to the initial designs in respect of TDDB at the price of moderately increased power consumption and delay.

Device scaling has enabled continuous performance increase of integrated circuits. However, severe reliability and yield concerns are arising against the background of nanotechnology. Traditionally, most causes and countermeasures were solely considered manufacturing issues, but lately, we have seen a shift towards operational reliability issues. Though, besides intense research on soft-errors and system-level approaches very little effort is put into low-level design solutions in order to enhance lifetime reliability. Hence, we demonstrate that redundant transistor insertion does improve system reliability significantly as regards Time-Dependent Dielectric Breakdown (TDDB). Furthermore, we introduce an algorithm which identifies the transistors being most vulnerable to TDDB. Subsequently, redundant transistors – called Shadow Transistors – are inserted at the previously identified instances. Lastly, we argue for applying high threshold voltage devices for the redundant transistors. Finally, we present results for a set of benchmark circuits and prove the combined approach successful. The enhanced designs were on average 41.8 % more reliable compared to the initial designs in respect of TDDB at the price of moderately increased power consumption and delay.

Related Publications

Sämrow, H.; Cornelius, C.; Sill, F.; Tockhorn, A.; Timmermann, D.,

Twin Logic Gates – Improved Logic Reliability by Redundance concerning Gate Oxide Breakdown

22nd Symposium on Integrated Circuits and Systems Design (SBCCI),

ISBN: 978-1-60558-705-9, pp. 315-320, Natal, Brazil, September 2009.

Sämrow, H.; Cornelius, C.; Sill, F.; Tockhorn, A.; Timmermann, D.

Automated Insertion of Twin Gates to improve Reliability concerning Gate Oxide Breakdown

SPIE Europe – Microtechnolgies for the New Millennium, ISBN: 978-0-81947-637-1, Dresden, Germany, May 2009.

Sämrow, H.; Cornelius, C.; Sill, F.; Tockhorn, A.; Timmermann, D.

Comparison of Strategies for Redundancy to improve Reliability concerning Gate Oxide Breakdown

Slides

Workshop für Testmethoden und Zuverlässigkeit von Schaltungen und Systemen – TuZ 2009, pp. 97-102, Bremen, Germany, February 2009.

Cornelius, C.; Sill, F.; Sämrow, H.; Salzmann, J.; Timmermann, D.; da Silva, D.

Encountering gate oxide breakdown with shadow transistors to increase reliability

Slides

21st Symposium on Integrated Circuits and Systems Design (SBCCI),

ISBN: 978-1-60558-231-3, pp. 111-116, Gramado, Brazil, September 2008.