Alternating Module Activation (AMA)

Reliability and robustness have been always important parameters of integrated systems. However, with the emergence of nanotechnologies reliability concerns are arising with an alarming pace. The consequence is an increasing demand of techniques that improve yield as well as lifetime reliability of to-day’s complex integrated systems. It is requested though, that the solutions result in only minimum penalties on power dissipation and system performance. The approach Alternating Module Activation (AMA) offers both extension of system lifetime and low increase of power and delay

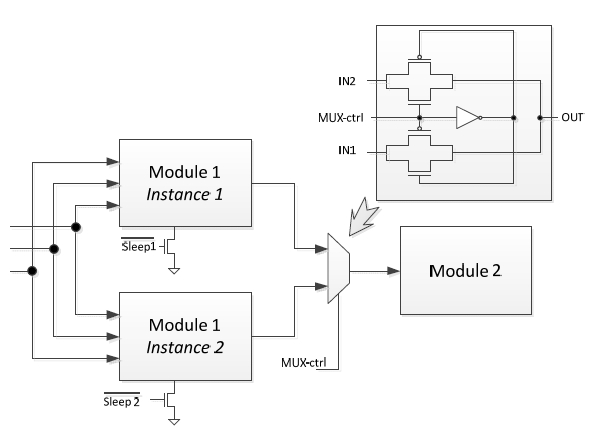

A notable characteristic of power gating with sleep transistors is the fact that the gated circuit can be almost completely disconnected from the power supply. Hence, in the disconnected state the gated circuit is nearly without any inherent currents and voltages. Additionally, the zero activity of the circuit reduces its temperature. Thus, in standby the three major parameters reducing the lifetime of integrated circuits are eliminated, or at least strongly reduced. Following, the mean time to a failure is extended approximately by the time the circuit is in standby. One way to extend the standby time is to improve the related algorithms. However, in designs with a high activity, as in streaming applications, medical environments, etc., the potential to extend the standby time is strongly limited. Thus, our proposed approach applies another way to extend the standby time of a gated module – redundant implementation. Thereby, each gated module is implemented at least two times. At runtime, only one of these instances is active while the others are disconnected from the power supply. In the ideal case, i.e. any additional control logic is omitted and the circuit is completely disconnected from the power supply. That means, for two instances and under ideal conditions the proposed approach doubles the MTTF. Compared to an ideal implementation of parallel module redundancy (PMR) the presented technique results in a MTTF which is 33 % higher. For four instances the improvement compared to PMR increases to 92 % which is already very close to the theoretical maximum of 100 %. It should be noted that the proposed technique is not limited to designs with high activity. In other words, the MTTF can be reduced also in systems with long standby periods in which all blocks are disconnected from the power supply. An additional advantage of the proposed approach is the extremely low increase of power dissipation. This follows from the fact that in theory at a given time at most one instance is active.

The main problem of the proposed approach is to ensure that the subsequent logic blocks receive the correct input data, i.e. the data from the currently active instance. This can be guaranteed by additional multiplexer. The latter are placed in front of the inputs of the logic blocks following the gated module and multiplex the outputs of all instances. Usually, power gated logic requires some clock cycles as wake-up time. Hence, it is not recommended to connect the signal controlling the sleep-transistor directly with the multiplexer’s control signal.

Related Publications

Sill Torres, F.;

Enhancement of System-Lifetime by Alternating Module Activation

IFIP Advances in Information and Communication Technology, v. 403, p. 82-91, 2013.

Cornelius, C.; Sill Torres, F. ; Timmermann, D.;

Power-Efficient Application of Sleep Transistors to Enhance the Reliability of Integrated Circuits

Journal of Low Power Electronics, ISSN 1546-1998, v. 7, nº 4, p. 552-561, 2011.

Sill Torres, F.; Cornelius, C.; Timmermann, D.;

Reliability Enhancement via Sleep Transistors

Slides

12th IEEE Latin-American Test Workshop (LATW),

ISBN: 978-1-4577-1490-0, Porto de Galinhas (PE), Brazil, March 2011.