Asynchronous Chain – True Single Phase Clock (AC-TSPC)

Asynchronous Chain – True Single Phase Clock (AC-TSPC) is a low power and robust circuit design technique invented by Dr. Frank Grassert.

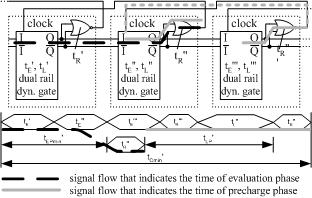

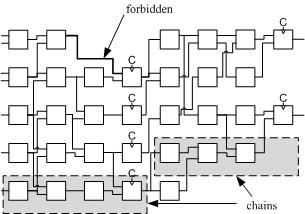

True single phase clock logic techniques, e.g. with alternating arranged N- and P-logic cells, yield easy to design circuits with standard cells and high speed potential. The disadvantages are a difficult clock tree design and high power consumption. To realize every logic function, dual rail or differential styles are chosen which increase clock load. We developed a method to speed up dynamic single clock circuits. The advantage of asynchronous logic is that the critical path delay is the sum of only the evaluation times of the single logic blocks without wasting time for waiting, latches, or redundant logic. Therefore, we assembles small asynchronous chains of dynamic logic blocks into one period of the global clock to minimize the unused time per clock cycle (AC-TSPC). However, the synchronous single phase clocking scheme is maintained. The advantages of this method are shorter latencies for calculations, power reduction by smaller clock trees and no need for latches, and a simpler clock distribution network due to increased clock skew tolerance. The results of the simulations of an 8×8 bit multiplier in TSPC and in AC-TSPC show an enhancement in power-reduction of 40% for the logic and of 89% for the clock tree with a latency reduction of 40% and more in comparison with TSPC.

Downloads

AC-DYNAMIC (Instructions)

pipelined Buffer – Netlist

pipelined ISCAS C1355 – Netlist

pipelined 4×4-Multiplier – Netlist

Please ask per Mail for: DYNAMIC (created by Dr. Andreas Wassatsch)

Related Publications

Sill, F.; Grassert, F.; Cornelius, C.; Timmermann, D.

A Design Tool for Modeling Asynchronous Dynamic Logic

Forschung und wissenschaftliches Rechnen: Beiträge zum Heinz-Billing-Preis 2006, GWDG-Bericht Nr. 72, ISSN: 0176-2516, Goettingen, Germany, November 2007.

Grassert, F.; Sill, F.; Cornelius, C.; Timmermann, D.

Verlustleistungsreduzierung bei dynamischen TSPC-Schaltungstechniken

Slides

35. GI-Jahrestagung: Workshop zum DFG-SPP: VIVA, ISBN: 3-88579-396-2, p. 450, Bonn, Germany, September 2005.

Grassert, F.,

Verlustleistungsoptimierte Schaltungstechniken für höchste Geschwindigkeiten

Phd. thesis, Rostock, Germany, 2005.

Sill, F.;Grassert, F,;Timmermann, D.

Reduzierung des Leistungsverbrauchs in Deep Submicron Designs

Slides

11. Symposium Maritime Elektrotechnik, Elektronik und Informationstechnik, Rostock, Germany, June 2004.

Sill, F.; Grassert, F.; Wassatsch, A.; Timmermann, D.

A Design Flow for Asynchronous Dynamic Logic and Standard Synthesis Tools

Slides

SNUG 2003 (nominated to receive the Technical Committee award for SNUG, Featured Article on Solvnet), Boston, MA, USA, September 2003.

Sill, F.;Grassert, F.;Wassatsch, A.;Timmermann, D.

Design flow zur Entwicklung Geschwindigkeits- und Leistungsoptimierter Schaltungen

Slides

4. IuK-Tage Mecklenburg-Vorpommern, Rostock, Germany, June 2003.

Grassert, F.; Sill, F.; Timmermann, D.

Verlustleistungsreduzierung in Datenpfaden

Slides

4. IuK-Tage Mecklenburg-Vorpommern, Rostock, Germany, June 2003.

Sill, F.:

Reduction of power dissipation in high frequency designs

GRK-Seminar, Rostock 2004.

Sill, F.:

Optimierungen an selbstgetakteten Einphasentakt-Schaltungen

Slides

Diplom, Rostock 2002.

Frank Grassert, Dirk Timmermann:

Single-Rail Self-timed Logic Circuits in Synchronous Designs

Slides

IEEE International Midwest Symposium on Circuits and Systems (MWSCAS’2002), Vol. I, S. 495-498, ISBN: 0-7803-7524-6, Tulsa – Oklahoma, USA, August 2002.