Mixed Gates

The idea behind the Mixed Gates design technique is the combination of advantages from gate level and transistor level approaches. That is, high accuracy and applicability for a standard cell design flow. In addition, the Mixed Gates approach merges both Dual Threshold Voltage-CMOS (DVT-CMOS) and Dual Tox-CMOS (DTO-CMOS) approaches.

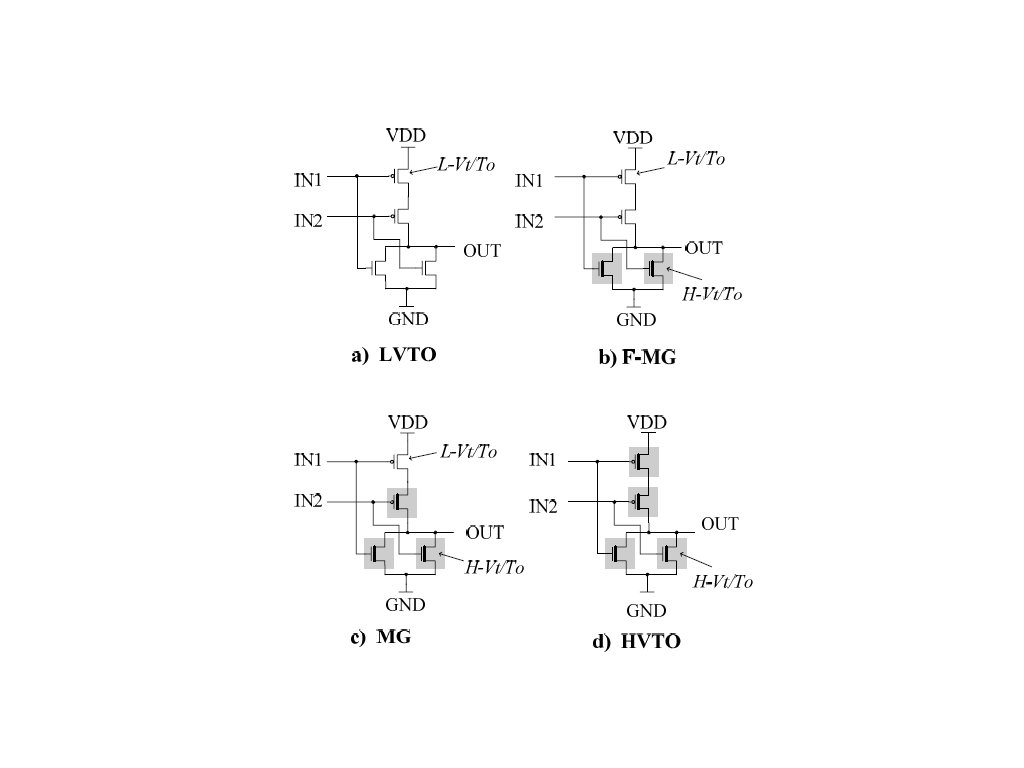

Transistor leakage as well as delay highly depends on the transistor parameters threshold voltage (Vth), gate oxide thickness (Tox), and channel depletion (NDEP). Against this background, two types of transistors were defined by extensive simulations. The first type, fast switching transistors L-Vt/To with high leakage currents, uses low Tox and low NDEP, which results in low Vth and short delay. The second transistor type H-Vt/To has high Tox and high NDEP, which results in high Vth. The latter transistors switch slower but have lower gate oxide leakage as well as reduced sub-threshold leakage. HVTO gates consisting solely of H-Vt/To transistors and LVTO gates consisting solely of L-Vt/To transistors have been implemented (see figure below). At this stage, leakage reduction based on the idea of DVT/DTO-CMOS approaches can be performed.

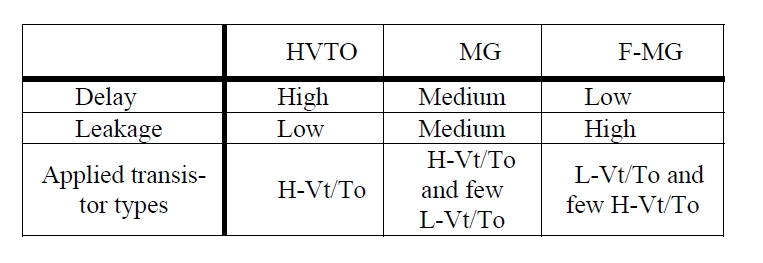

However, the Mixed Gates approach offers two additional gate types, which are called standard Mixed Gates (MG) and Fast Mixed Gates (F-MG). F-MG gates contain few H-Vt/To transistors at adequate positions so that delay is equal to corresponding LVTO gates but leakage is lower. Therefore, LVTO gates are not used any further because they can be replaced by F-MG gates without any drawback on performance due to equal delay but lower leakage. Finally, MG gates contain mainly H-Vt/To transistors, so that gate delay is in between the delay of F-MG and HVTO gates. The figure above depicts four variations of a NOR2 gate and the table classifies mixed gate types qualitatively. When applying the Mixed Gates approach, a design is initially implemented with F-MG gates only. Then, as many gates as possible are exchanged by appropriate MG and HVTO gates so that maximum delay is not increased. That is, critical paths consist solely of F-MG gates whereas all other paths apply a combination of the three gate types so that path delays do not exceed critical path delay.

Thus, the Mixed Gates approach offers three advantages:

- larger amount of low leakage devices within a design than possible in DVTO approaches

- reduction of both main sources of leakage currents: gate oxide leakage Igate and sub-threshold leakage Isub

- no drawback on performance compared to the original designs which consist of fast and high leakage devices

Related Publications

Sill Torres, F.,

Improvement of Technology Parameters for a Dual-Vth/Tox Technology

SEMINATEC 2012, São Bernardo do Campo, Brazil, April 2012.

Sill. F.,

Untersuchung und Reduzierung des Leckstroms integrierter Schaltungen in Nanometer-Technologien bei konstanten Performanceanforderungen

Grin Verlag, ISBN: 978-3-640-22741-9, Germany, 2009

Sill, F.; Cornelius, C.; Timmermann, D.,

Leckstromreduzierung in Nanometer-Technologien ohne Performanceverluste,

Slides

12. Symposium Maritime Elektrotechnik, Elektronik und Informationstechnik, pp. 329-334, Rostock, Germany, October 2007.

Salomon, R.; Sill, F.,

High-speed, low-leakage integrated circuits: An evolutionary algorithm perspective,

Journal of systems architecture, ISSN 1383-7621, vol. 53-2007, 5, pp. 321-327, Amsterdam: Elsevier, Netherlands, May 2007.

Sill, F.; Jiaxi, Y.; Timmermann, D.,

Design of Mixed Gates for Leakage Reduction,

Slides

2007 Great Lakes Symposium on VLSI (GLSVLSI), pp.263-268, ISBN: 978-1-59593-605-9, Stresa-Lago Maggior, Italy, March 2007.

Salomon, R.; Sill, F.; Timmermann, D.,

Minimizing Leakage: What if every gate could have its individual threshold voltage?,

Artificial Intelligence and Applications (AIA 2007), pp. 492-497, ISBN: 978-0-88986-629-4, Innsbruck, Austria, February 2007.

Engel, K.; Kalinowski, T.; Labahn, R.; Sill, F.; Timmermann, D.,

Algorithms for Leakage Reduction with Dual Threshold Design Techniques,

Slides

International Symposium on System-on-Chip 2006, pp.111-114, ISBN: 1-4244-0621-8, Tampere, Finland, November 2006.

Sill, F.; Cornelius, C.; Kubisch, S.; Timmermann, D.,

Mixed Gates: Leakage Reduction techniques applied to Switches for Networks-on-Chip,

Slides

2nd Reconfigurable Communication-centric SoCs (ReCoSoC) Workshop 2006, pp.76-82, ISBN: 2-9517461-2-1, Montpellier, France, July 2006.

Sill, F.; Salomon, R.,

Evolving High-Speed, Energy-Efficient Integrated Circuits,

IEEE World Congress on Computational Intelligence (WCCI 2006), pp. 3121-3128, ISBN: 0-7803-9487-9, Vancouver, Canada, June 2006.

Salomon, R.; Sill, F.,

Biologically-Inspired Optimization of Circuit Performance and Leakage: A Comparative Study,

ARCS’06: Architecture of Computing Systems, pp. 352-366, ISBN: 3-8857-9175-7, Frankfurt/Main, Germany, March 2006.

Sill, F.; Cornelius, C.; Timmermann, D.,

Statistische Analyse des Zeitverhaltens von CMOS Schaltungen und Modellierung von Parametervariationen,

Slides

18th Workshop Testmethoden und Zuverlaessigkeit von Schaltungen und Systemen, pp. 117-118, Titisee-Neustadt, Germany, March 2006.

Sill, F.; Cornelius, C.; Timmermann, D.,

Reduzierung des Leckstromverbrauchs mit gemischten Gattern in Deep Submicron Technologien

Slides

9. Workshop Methoden und Beschreibungssprachen zur Modellierung und Verifikation von Schaltungen und Systemen, ISBN: 3-9810287-1-6, pp. 275-283, Dresden, Germany, February 2006.

Sill, F.;Timmermann, D.,

Total Leakage Reduction by Observance of Parameter Variations

Slides

23rd Norchip Conference, ISBN: 1-4244-0064-3, pp. 261-264, Oulu, Finland, November 2005.

Sill, F.;Grassert, F.;Timmermann, D.,

Total leakage power optimization with improved Mixed Gates

Slides

18th Symposium on Integrated Circuits and Systems Design (SBCCI 2005), pp. 154-159, ISBN: 1-59593-174-0, Florianopolis, Brazil, September 2005.

Sill, F.;Timmermann, D.; Cornelius, C.

Modeling of Total Parameter Variations

Slides

8th Euromicro Conference on Digital System Design, ISBN: 3-902457-09-0, pp.6-7, Porto, Portugal, September 2005.

Engel, K.; Kalinowski, T.; Labahn, R.; Sill, F.; Timmermann, D.

Optimization of Dual-Threshold Circuits

Preprint, ISSN 0948-1028, Rostock, Germany, May 2005.

Sill, F.;Grassert, F.;Timmermann, D.:

Reducing Leakage with Mixed-Vth (MVT)

Slides

18th Conference on VLSI Design, pp. 874-877, ISBN: 0-7695-2264-5, Kolkata, India, January 2005.

Sill, F.;Grassert, F,;Timmermann, D.

Low Power Gate-level Design with Mixed-Vth (MVT) Techniques

Slides

17th Symposium on Integrated Circuits and Systems (SBCCI), pp. 278-282, ISBN: 1-58113-947-0, Porto de Galinhas, Brazil, September 2004.

Sill, F.;Grassert, F,;Timmermann, D.

Reduzierung des Leistungsverbrauchs in Deep Submicron Designs

Slides

11. Symposium Maritime Elektrotechnik, Elektronik und Informationstechnik, Rostock, Germany, June 2004.